题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

用ISP技术设计一个可控计数器,控制信号为X.当X=0时,实现模4计数;当X=1时,实现模8计数.请用VHDL语言写出设计源文件.

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“用ISP技术设计一个可控计数器,控制信号为X.当X=0时,实…”相关的问题

更多“用ISP技术设计一个可控计数器,控制信号为X.当X=0时,实…”相关的问题

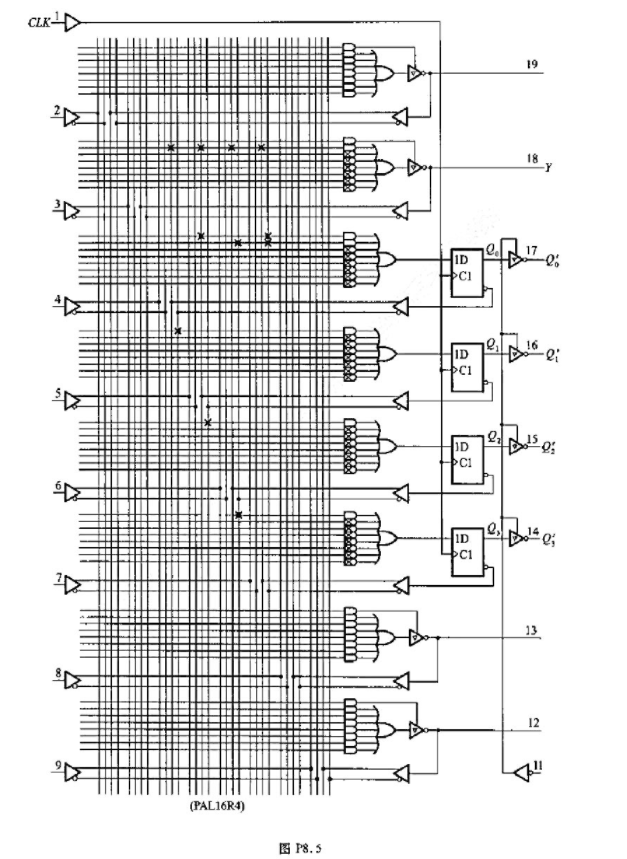

用一片如图A1-4所示的4位二进制加法计数器74161和必要的逻辑门电路设计一个可控计数器,要求当控制信号M=1时,实现七进制计数器;而当控制信号M=0时,实现十三进制计数器。画出所设计的可控计数器的逻辑电路。

设计一个可控同步计数器,M1、M2为控制信号,要求:

(1)M1M2=00时,维持原状态;

(2)M1M2=01时,实现模2计数;

(3)M1M2=10时,实现模4计数;

(4)M1M2=11时,实现模8计数。