更多“十六路数据选择器,其地址输入(选择控制输入)端有()个.”相关的问题

更多“十六路数据选择器,其地址输入(选择控制输入)端有()个.”相关的问题

第9题

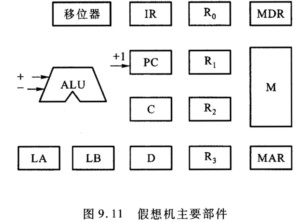

某假想机主要部件如图9.11所示,其中: LA ALU的A输入端选择器 LB ALU的B输

入端选择器 M 主存 MDR 主存数据寄存器 IR 指令寄存器 MAR 主存地址寄存器 PC 程序计数器 R0~R3 通用寄存器 C、D 暂存器

点击查看答案

(1)补充各种部件之间的主要连接线,并注明数据流动方向。 (2)写出ADD @R1,@R2和SUB @R1,@R2指令取指阶段和执行阶段的信息流程。R1寄存器中存放源操作数的地址,R2寄存器中存放的是目的操作数的地址。

(1)补充各种部件之间的主要连接线,并注明数据流动方向。 (2)写出ADD @R1,@R2和SUB @R1,@R2指令取指阶段和执行阶段的信息流程。R1寄存器中存放源操作数的地址,R2寄存器中存放的是目的操作数的地址。

第10题

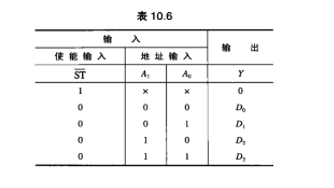

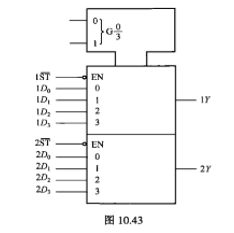

试用双4选1数据选择器74153和少量门设计一个有4个输入X3、X2、X1、X0和2个输出Y≇

试用双4选1数据选择器74153和少量门设计一个有4个输入X3、X2、X1、X0和2个输出Y1、Y0的逻辑电路.电路输入为余3BCD码,输出为用2位二进制数表示的输入码中“1”的个数,例如,当输入X3X2X1X0=1010时,输出Y1Y0=10.当非余3码(伪码)输入时,要求输出Y1Y0=00.要求写出设计过程,画出电路图(规定X3、X2分别和数据选揮器地址码的高、低位相连接,74153的逻辑符号和功能表分别如图10.43和表10.6所示).

如果结果不匹配,请

如果结果不匹配,请