题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

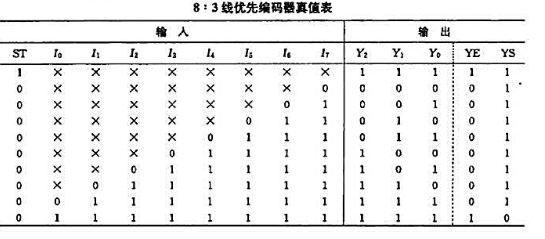

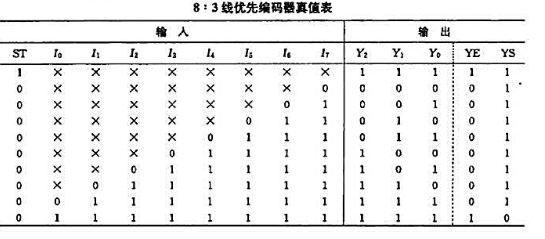

8:3线优先编码器真值表如下表所示,其中l0~I7为数据输入端(优先级I7为最高),ST为使

8:3线优先编码器真值表如下表所示,其中l0~I7为数据输入端(优先级I7为最高),ST为使能输入端,Y0~Y2为数据输出端,YE、YS为输出扩展端.用VHDL语言设计之.

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

8:3线优先编码器真值表如下表所示,其中l0~I7为数据输入端(优先级I7为最高),ST为使能输入端,Y0~Y2为数据输出端,YE、YS为输出扩展端.用VHDL语言设计之.

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“8:3线优先编码器真值表如下表所示,其中l0~I7为数据输入…”相关的问题

更多“8:3线优先编码器真值表如下表所示,其中l0~I7为数据输入…”相关的问题

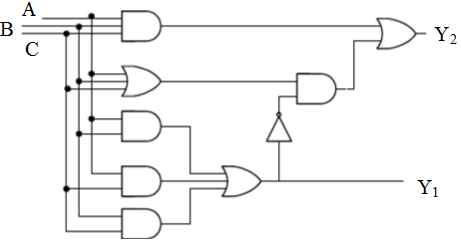

74148是8线-3线优先编码器,其真值表如表所示。在图所示各电路中,确定输出A0,OE,IE,GS,YS的值。

| 输 入 | 输 出 |

| overline{S_{T}}overline{I}_{1}overline{I}_{1}overline{I}_{2}overline{I}_{3}overline{I}_{4}overline{I}_{5}overline{I}_{6}overline{I}_{7} | overline{Y}_{2}overline{Y}_{1}overline{Y}_{0}overline{Y}_{EX}YS |

| 1 × × × × × × × × 0 1 1 1 1 1 1 1 1 0 × × × × × × × 0 0 × × × × × × 0 1 0 × × × × × 0 1 1 0 × × × × 0 1 1 1 0 × × × 0 1 1 1 1 0 × × 0 1 1 1 1 1 0 × 0 1 1 1 1 1 1 0 0 1 1 1 1 1 1 1 | 1 1 1 1 1 1 1 1 1 0 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 0 1 1 0 0 0 1 1 0 1 0 1 1 1 0 0 1 1 1 1 0 1 |

优先编码器74HC147的功能表如下表所示,试用74HC147和适当的门构成输入为低有效的 ,输出为8421BCD码,并具有编码输出标志的编码器。

,输出为8421BCD码,并具有编码输出标志的编码器。

| 输入 | 输 出 |

| overline{I_{1}}overline{I_{2}}overline{I_{3}}overline{I_{4}}overline{I_{5}}overline{I_{6}}overline{I_{7}}overline{I_{8}}overline{I_{9}} | overline{Y_{3}}overline{Y_{2}}overline{Y_{1}}overline{Y_{0}} |

| H H H H H H H H H × × × × × × × × L × × × × × × × L H × × × × × × L H H × × × × × L H H H × × × × L H H H H × × × L H H H H H × × L H H H H H H × L H H H H H H H L H H H H H H H H | H H H H L H H L L H H H H L L L H L L H H L H L H L H H H H L L H H L H H H H L |

试画出用4片8线-3线优先编码器74HC148组成32线-5线优先编码器的逻辑图。74HC148的逻辑图见图4.8.1。允许附加必要的门电路。

A.000

B.010

C.101

D.111

某地区年粮食总产量如下表所示:

| 年份 | 产量(万吨) | 年 份 | 产量(万吨) |

| 1 2 3 4 5 | 230 236 241 246 252 | 6 7 8 9 10 | 257 262 276 281 286 |

要求:

A.进度延误15%,费用超支15%,发生几率为0.5

B.进度延误15%,费用超支30%,发生几率为0.2

C.进度延误15%,费用超支25%,发生几率为0.3

D.进度延误25%,费用超支15%,发生几率为0