题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

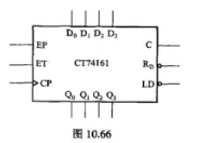

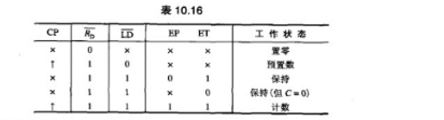

位二进制同步计数器T1161及双4选1多路数据选择器T4153的功能表及逻辑符号如图7.2.12所示,试用其

1.jpg)

答案

答案

(a)因为序列信号长度为7用T1161构成模7计数器。为此令预置数据D3D2D1D0=1001进位输出C经非门反相连至3.jpg)

本例要求产生两组循环长度为7位的序列发生器,故应采用计数器型序列发生器结构。由T1161构成模7计数器,而由T4153实现组合电路。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

1.jpg)

答案

答案

(a)因为序列信号长度为7用T1161构成模7计数器。为此令预置数据D3D2D1D0=1001进位输出C经非门反相连至3.jpg)

本例要求产生两组循环长度为7位的序列发生器,故应采用计数器型序列发生器结构。由T1161构成模7计数器,而由T4153实现组合电路。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“位二进制同步计数器T1161及双4选1多路数据选择器T415…”相关的问题

更多“位二进制同步计数器T1161及双4选1多路数据选择器T415…”相关的问题

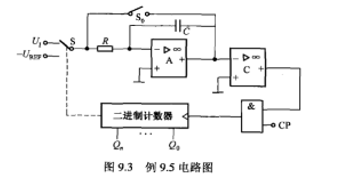

双积分A/D转换电路如图9.3所示,试回答下列问题:

(1)若被测电压的峰值UImax=2V,要求分辨率≤0.1mV,则二进制计数器总容量应大于多少?

(2)需要多少位二进制计数器?

(3)若时钟脉冲频率fCP=200kHz,则采样保持时间为多少?

(4)若时钟脉冲频率fCP=200kHz, ,积分器输出电压Uo的最大值为5V,问积分时间常数RC为多少?

,积分器输出电压Uo的最大值为5V,问积分时间常数RC为多少?

如图所示逻辑电路由CT74161(同步四位二进制计数器)和CT74151(八选一数据选择器)组成。

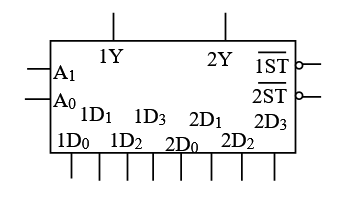

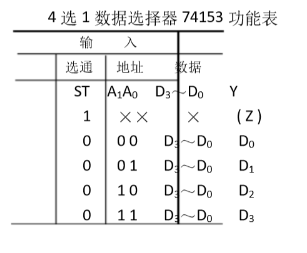

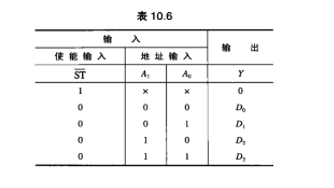

出设计过程,画出逻辑电路。4选1数据选择器功能表和符号图分别见功能表和附图。

试以同步二进制计数器74161为核心设计一个模10计数器,要求计数器按下列规律技术,并要求:(1)电路具有开机清零功能;(2)写出电路设计过程并画出完整电路图(电路设计可加门和MSI组合逻辑电路)。

0,1,3,5,7,9,2,4,6,8,0,1,3,…

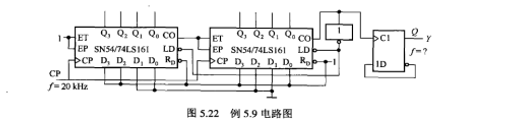

由两片SN54/74LS161(同步4位二进制计数器)组成的同步计数器如图5.22所示.

1)试分析其分频比(即Y与CP之频比),当CP的频率为20kHz时,Y的频率为多少?

2)试用2片SN54/74LS161组成模为91的计数器,要求两片间用级联法,并工作可靠.

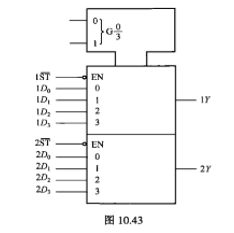

试用双4选1数据选择器74153和少量门设计一个有4个输入X3、X2、X1、X0和2个输出Y1、Y0的逻辑电路.电路输入为余3BCD码,输出为用2位二进制数表示的输入码中“1”的个数,例如,当输入X3X2X1X0=1010时,输出Y1Y0=10.当非余3码(伪码)输入时,要求输出Y1Y0=00.要求写出设计过程,画出电路图(规定X3、X2分别和数据选揮器地址码的高、低位相连接,74153的逻辑符号和功能表分别如图10.43和表10.6所示).

位二进制加法计数器CT74161和集成单稳态触发器CT74LS121组成如图P6.10(a)所示的电路.

(1)分析CT74161组成电路,画出转换状态图.

(2)估算CT74LS121组成电路的输出脉宽Tw值.

(3)设CP为方波(周期Td≥1ms),在图P6.10(b)中画出图P6.10(a)中u1、u0两点的工作波形.