题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

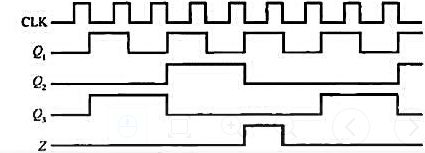

设计一个计数器,在CLK脉冲作用下,三个触发器Q1、Q2、Q3及输出Z的波形图如图3.27所示

,用JK触发器实现.Q3为高位,Q1为低位.

图3.27

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

图3.27

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“设计一个计数器,在CLK脉冲作用下,三个触发器Q1、Q2、Q…”相关的问题

更多“设计一个计数器,在CLK脉冲作用下,三个触发器Q1、Q2、Q…”相关的问题

由16×4位ROM和4位二进制加法计数器74LS161组成的脉冲分配电路如图7-13所示,ROM输入和输出关系如表7-4所示。试画出在CLK信号作用下D3、D2、D1、D0的波形。

表7-4 R0M输入和输出关系 | |||||||

| 地址输入 | 数据输出 | ||||||

| A3 | A2 | A1 | A0 | D3 | D2 | D1 | D0 |

| 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 | 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 | 1 0 0 0 0 1 1 1 1 1 0 0 0 0 0 0 | 1 0 0 1 1 0 0 0 1 1 0 0 0 1 1 0 | 1 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 | 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 |

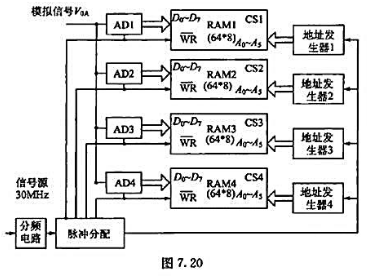

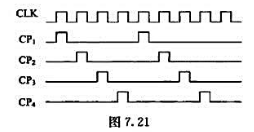

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如图7.20所示.系统信号源为30MHz的方波,时钟信号CLK为10MHz(要求占空比为1:1).并行交替式数据采集系统利用4片ADC轮流对同一个模拟输入信号进行采样,分别存人各路对应的64单元的存储器中,其对应各路AD所需的采样信号波形如图7.21所示,脉冲分配电路可用计数器+译码器构成.试根据系统设计参数要求,完成各部分电路的设计,器件任选.

(1)分频电路;

(2)脉冲分配电路;

(3)地址发生器电路设计;

(4)说明每个地址发生器所使用的时钟信号分别是什么?

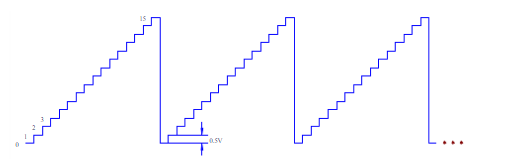

用D/A转换芯片DAC0832和4位二进制计数器芯片74LS161,设计一个阶梯脉冲发生器。要求有15个阶梯,每个阶梯高0.5V,如图T11.2-1所示。请选择参考电源VREF,并画出电路连线图。