更多“设计一个译码电路,将表1.2.1中的2421码转换为表1.2…”相关的问题

更多“设计一个译码电路,将表1.2.1中的2421码转换为表1.2…”相关的问题

第3题

设计一个对2F8H进行读写操作的端口译码电路,要求分别用:(1)门电路,(2)门电路和74LS138译码器。

设计一个对2F8H进行读写操作的端口译码电路,要求分别用:(1)门电路,(2)门电路和74LS138译码器。

点击查看答案

第6题

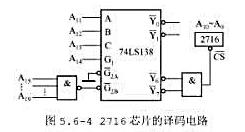

有一个EPROM2716(2Kx8b)芯片的译码电路,如图5.6-4所示,请计算该芯片的地址范围。

有一个EPROM2716(2Kx8b)芯片的译码电路,如图5.6-4所示,请计算该芯片的地址范围。

点击查看答案

第8题

综合是EDA设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;在下面对综合的描述中()是错误的。

A.综合就是将电路的高级语言转化成低级的,可与FPGA/ CPLD的基本结构相映射的网表文件

B.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束

C.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的

D.综合是纯软件的转换过程,与器件硬件结构无关

第9题

综合是EDA设计的关键步骤,下面对综合的描述中错误的是()。

A.综合就是把抽象设计中的一种表示转换成另一种表示的过程

B.综合就是将电路的高级语言转换成低级的,可与FPGA/CPLD相映射的功能网表文件

C.综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的

D.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束

如果结果不匹配,请

如果结果不匹配,请