题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

用触发器和门电路设计一个2421码的十进制计数器。请标明计数输入端和进位输出端。计数过程中2421码的变化顺序如表1.2.1中所示。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“用触发器和门电路设计一个2421码的十进制计数器。请标明计数…”相关的问题

更多“用触发器和门电路设计一个2421码的十进制计数器。请标明计数…”相关的问题

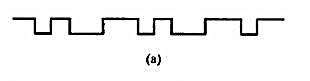

利用D触发器构成的移位寄存器配合适当的门电路,设计产生图3.26(a)所示的脉冲序列信号发生器.