题目内容

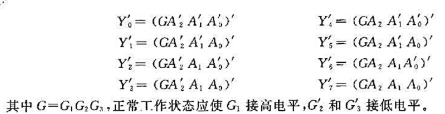

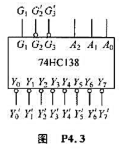

(请给出正确答案)

题目内容

(请给出正确答案)

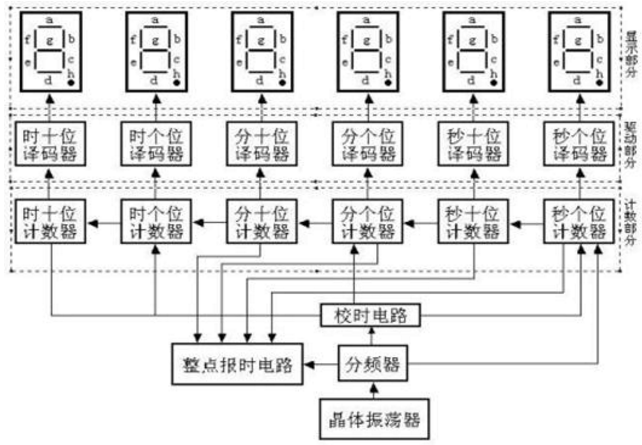

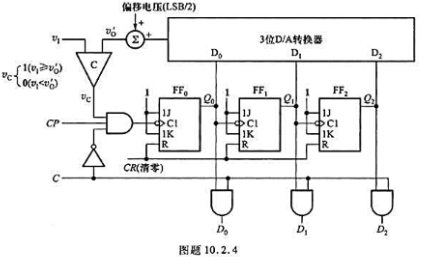

试设计一个数字电子钟,其原理框图如图9-10所示。秒信号用石英晶体振荡器(频率为32768Hz)加分频器来实现。译码

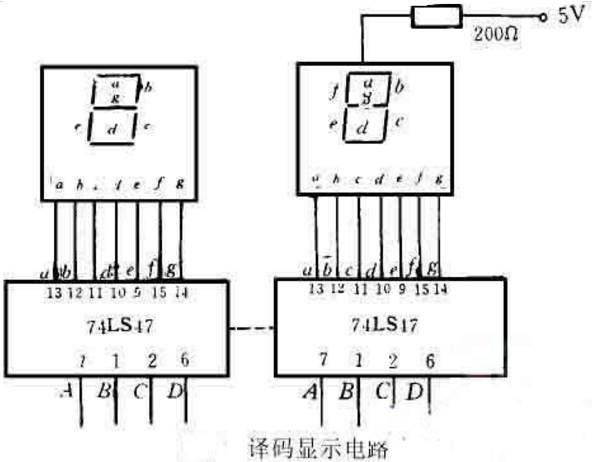

试设计一个数字电子钟,其原理框图如图9-10所示。秒信号用石英晶体振荡器(频率为32768Hz)加分频器来实现。译码显示电路将“时”、“分”、“秒”计数器的输出状态经七段显示译码器译码,通过6位LED七段显示器显示出来。整点报时电路是根据计时系统的输出状态产生一个脉冲信号,然后去触发音频发生器实现报时。校时电路是用来对“时”、“分”、“秒”显示数字进行校对调整的。

答案

答案

1)总体设计与实现

根据题意和图9-10给出的原理框图,秒信号是整个系统的时基信号,它直接决定着计时系统的精度,一般用石英晶体振荡器加分频器来实现。将标准的秒信号送入“秒计数器”,“秒计数器”采用六十进制计数器,每累计60秒发出一个“分”脉冲信号,该信号将作为“分计数器”的时钟脉冲。“分计数器”也采用六十进制计数器,每累计60分,发出一个“时”脉冲信号,该信号将被送到“时计数器”。“时计数器”采用二十四进制计数器,可实现对一天24小时的累计。整点报时电路是根据计时系统的输出状态产生脉冲信号,然后去触发音频发生器实现报时。

用VHDL语言实现上述要求的电路框图如图9-11所示,本系统由8个部分组成,分别为校时控制器、时钟分频器、秒计数器、分计数器、时计数器、译码电路、显示模块和整点报时电路。下面简要介绍它们的功能。

·校时控制器(control):获取对时、分、秒校对的控制选通信号;

·时钟分频器(fre):从晶体振荡器获取1Hz的时钟信号;

·秒计数器(second):六十进制计数器;

·分计数器(minute):六十进制计数器;

·时计数器(hour):二十四进制计数器;

·译码电路(decoder):将时、分、秒的6位二进制数转换为2个十进制的数;

·显示模块(display):将译码电路的输出在七段数码管上显示;

·整点报时电路(alarm):针对当前时间,输出报时信号。

实现功能的顶层VHDL源程序如下:

1 LIBRARY IEEE;

2 USE IEEE. STD_LOGIC_II64. ALL;

3 USE IEEE. STD LOGIC SIGNED. ALL;

4

5 ENTITY digtal_watch IS

6 PORT(

7 clk: IN STD_LOGIC;

8 clr : IN STD_LOGIC;

9 en : IN STD_LOGIC;

10 timeselect: IN STD_LOGIC;

11 displaysecondten, display_second_one : OUT STD_LOGIC_VECTOR( 6 DOWNTO 0 ) ;

12 display_minute_ten, display_minute_one : OUT STD_LOGIC_VECTOR( 6 DOWNTO 0 ) ;

13 display_hour_ten, display_hour_one : OUT STD_LOGIC_VECTOR (6 DOWNTO 0 ) ;

14 F1, F2 : OUT STD_LOGIC

15 );

16 END digtal_watch;

17

18 ARCHITECTURE arch_digtal_watch OF digtal_watch IS

19

20 COMPONENT fre IS

21 PORT

22 (

23 clr:IN STD LOGIC;

24 clk in:IN STD LOGIC; --时钟输入信号

25 clk out:OUT STD LOGIC --分频后输出时钟信号

26 );

27 END COMPONENT;

28

29 COMPONENT second IS

30 PORT(

31 clk in : IN STD_LOGIC;

32 clr : IN STD_LOGIC;

33 cs : IN STD_LOGIC;

34 second led out : OUT STD_LOGIC VECTOR(5 DOWNT0 0) ;

35 clk_second to minute : OUT STD LOGIC ; --秒向分钟模块的进位信号

36 second_alarm1: OUT STD_LOGIC; --报警控制输出信号1

37 second_alarm2: OUT STD_LOGIC --报警控制输出信号2

38 );

39 END COMPONENT;

40

41 COMPONENT minute IS

42 PORT(

43 clk_in : IN STD_LOGIC;

44 clr : IN STD_LOGIC;

45 cs : IN STD_LOGIC;

46 minute led out : OUT STD_LOGICVECTOR(5 downto 0);

47 elk minute to hour : OUT STD_LOGIC; --向小时模块的进位

48 minute alarm: OUT STD LOGIC

49 );

50 END COMPONENT;

51

52 COMPONENT hour IS

53 PORT(

54 elk_in:IN STD_LOGIC; --时钟

55 clr:IN STD_LOGIC;

56 as:IN STD_LOGIC; --片选

57 hour_led_out:OUT STD_LOGIC_VECTOR(5 downto 0) --小时输出显示

58 );

59 END COMPONENT;

60

61 COMPONENT control IS

62 PORT

63 (

64 en : IN STD_LOGIC; --全局使能信号

65 time select : IN STD_LOGIC; --时钟调整信号

66 clr : IN STD_LOGIC; --清零信号

67 cs_second : OUT STD_LOGIC; --片选秒校对信号

68 as_minute : OUT STD_LOGIC; --片选分校对信号

69 cs_hour : OUT STD_LOGIC --片选小时校对信号

70 );

71 END COMPONENT;

72

73 COMPONENT decoder IS

74 PORT(

75 data:IN STD_LOGIC_VECTOR(5 DOWNTO 0) --输入数据

76 ten:OUT STD_LOGIC_VECTOR(3 DOWNTO 0) --十位数据

77 one: OUT STD_LOGIC VECTOR ( 3 DOWNT0 0 ) --个位数据

78 );

79 END COMPONENT;

80

81 COMPONENT display IS

82 PORT(

83 data:IN STDLOGIC_VECTOR(3 DOWNT0 0)

84 play:0UT STD_LOGIC_VECTOR(6 DOWNT0 0

85 );

86 END COMPONENT;

87

88 COMPONENT alarm IS

89 PORT

90 (

91 minute_alarm:IN STD_LOGIC;

92 second alarm1:IN STD_LOGIC;

93 second alarm2:IN STD_LOGIC;

94 FI:OUT STD_LOGIC;

95 F2:OUT STD LOGIC

96 );

97 END COMPONENT;

98

99 SIGNAL control_second, control_minute, control hour:STD_LOGIC;

100 SIGNAL cs_second, cs_minute, cs_hour:STD_LOGIC;

101 SIGNAL clk_1hz:STD_LOGIC;

102 SIGNAL second_led, minute_led, hour_led:STD_LOGIC_VECTOR(5 DOWNTO 0);

103 SIGNAL clksecond to minute, clk_minute to hour:STD_LOGIC;

104 SIGNAL second_ten, second_one, minute_ten, minute_one,

105 hour_ten, hour_one:STD_LOGIC_VECTOR(3 DOWNT0 0);

106 SIGNAL minute_alarm, second alarm1,second alarm2:STD_LOGIC;

107

108 BEGIN

109

110 PROCESS(elk)

111 BEGIN

112

113 IF(clk'event andclk = '1')THEN

114 IF(control_second = '1')THEN

115 cs second< = '1';

116 ELSE

117 cs second< = '0';

118 END IF;

119

120 IF(control_minute = '1'or clk_second to_minute = '1')THEN

121 cs minute< = '1';

122 ELSE

123 cs minute< = '0';

124 END IF;

125

126 IF(control_hour = '1'or clk_minute_to_hour = '1')THEN

127 cs hour< = '1';

128 ELSE

129 cs hour< = '0';

130 END IF;

131 END IF;

132

133 END PROCESS;

134

135 u0: control PORT MAP(en = > en, time_select = > time_select,

136 clr = > clr, es_second : > control_second, cs minute = > control_minute,

137 cs_hour = > control_hour);

138 u1: fre PORT MAP(clr=>clr, clk_in=>clk, clk out=>clk_1hz);

139 u2: second PORT MAP(clk_in = > clk_1hz, clr = >elr, cs = > cs_second,

140 second led out = > second_led,

141 clk_second_to_minute = > clk_second_to_minute,

142 second_alarm1 = > second_alarm1, second_alarm2 = > second_alarm2);

143 u3: minute PORT MAP(clk_in = > clk_1hz, clr = > clr, cs = > cs_minute,

144 minute led_out = > minute_led,

145 clk_minute_to_hour=>clk_minute to hour,

146 minute_alarm = > minute_alarm);

147 u4: hour PORT MAP(clk_in=>clk_1hz, clr=>clr, cs =>cs_hour,

148 hour_led_out = > hour_led);

149 u5: decoder PORT MAP(data = > second_led, ten = > second_ten, one = > second_one);

150 u6: display PORT MAP(data = > second_ten, play = > displaysecond_ten);

151 u7: display PORT MAP(data = > second_one, play = > display_second_one);

152 u8: decoder PORT MAP(data = > minute_led, ten = > minute_ten, one = > minute_one);

153 u9: display PORT MAP(data = > minute_ten, play = > display minute_ten);

154 u10: display PORT MAP(data = > minute_one, play = > display_minute_one);

155 u11: decoder PORT MAP(data = > hour_led, ten = > hour_ten, one = > hour_one);

156 u12: display PORT MAP(data = > hour_ten, play = > display_hour_ten);

157 u13: display PORT MAP(data = > hour_one, play = > display_hour_one);

158 u14: alarm PORT MAP(minute_alarm = > minute_alarm,

159 second_alarm1 = > second_alarm1,

160 second_alarm2 = > second_alarm2,

161 F1 =>F1, F2=>F2);

162 END arch_digtal_watch;

2)校时控制器

校时控制器有3个输入变量和3个输出变量,如图9-12所示。3个输入变量是:en使能输入、clr清零和time_select时钟选择。3个输出变量是:cs_second秒时钟选择、cs_minute分时钟选择和cs_hour小时时钟选择。

在程序实现时,设置一个2位中间信号量cs_time,作为对时、分、秒校对的选择信号。当cs_time为00时,选择对“秒”进行调整;当cs_time为01时,选择对“分”进行调整;当cs_time为10时,选择对“时”进行调整。 校时控制器的VHDL源程序如下:

校时控制器的VHDL源程序如下:

1 LIBRARY IgEg;

2 USE IEEE. STD_LOGIC_II64.ALL;

3 USE IEEE. STD_LOGIC_SIGNED. ALL;

4 ENTITY control IS

5 PORT

6 (

7 en: IN STD_LOGIC; --全局使能信号

8 time——select : IN STD_LOGIC; --时钟调整信号

9 clr : IN STD_LOGIC; --清零信号

10 cs_second : OUT STD_LOGIC; --片选秒校对信号

11 cs_minute : OUT STD_LOGIC; --片选分校对信号

12 cs_hour : OUT STD LOGIC --片选小时校对信号

13 );

14 END control;

15 ARCHITECTURE control architecture OF control IS

16 SIGNAL cs_time : STD_LOGIC_VECTOR( 1 DOWNTO 0 ) ;

17 BEGIN

18 PROCESS( elr, time_select)

19 BEGIN

20 IF(clr = '0' ) THEN

21 cs time<= "00";

22 ELSIF(time_select'event and time_select= '1')THEN

23 IF(en= '1') THEN

24 cs_time < = cs_time + '1';

25 END IF;

26 IF(cs_time = "11" )THEN

27 cs time<= "00";

28 END IF;

29 END IF;

30 END PROCESS;

31 PROCESS (cs_time)

32 BEGIN

33 CASE cs time is

34 when "00" = > cs_hour < = '0 --校秒

35 cs_minute< = '0'7

36 cs_second < = '1';

37 when "01" = > cs_hour< = '0'; --校分

38 cs_minute < = '1';

39 cs_secomd < = '0';

40 when "10" = > cs hour<= '1'; --校时

41 cs_minute < = '0';

42 cs_second < = '0';

43 when others = >cs hour<= '0';

44 cs_minute < = '0';

45 cs_second < = '0';

46 END CASE;

47 END PROCESS;

48 END control_architecture;

校时控制器的仿真时序。

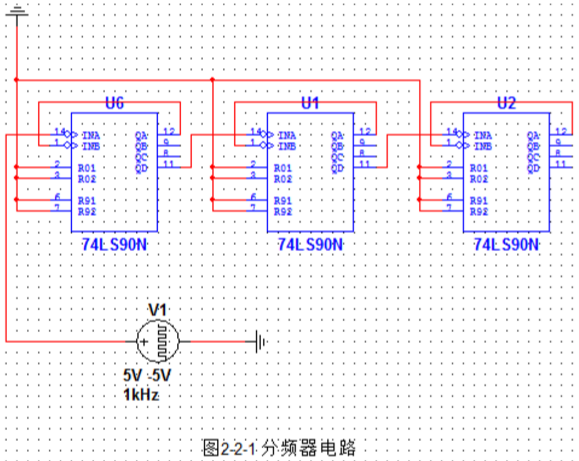

3)时钟分频器

时钟分频器是数字电子钟基准脉冲信号(秒信号)产生器。根据题目要求,要用石英晶体振荡器产生32768Hz输入信号。为了得到1Hz的秒脉冲信号,需要对32768Hz脉冲信号进行215分频,可用15位二进制计数器实现。如果用逻辑器件实现可选用1片14位二进制计数器CD4060和1片D触发器。下面用VHDL模拟CD4060和D触发器实现215分频。

时钟分频器由2个输入和1个输出组成,如图2所示。

时钟分频器的VHDL源程序如下:

1 LIBRARY IEEE;

2 USE IEEE. STD_LOGIC_II64.ALL;

3 USE IEEE. STD_LOGIC_SIGNED. ALL;

4

5 ENTITY fre IS

6 PORT

7 (

8 clr : IN STD LOGIC;

9 clk_in : IN STD_LOGIC; --时钟输入信号

10 clk_out : OUT STD_LOGIC --分频后输出时钟信号

11 );

12 END fre;

13 ARCHITECTURE fre architecture OF fre IS

14 SIGNAL timetempl,time_temp2:STD_LOGIC;

15 BEGIN

16 PROCESS(clk_in, clr)

17 VARIABLE count:INTEGER RANGE 0 TO 16384; --32768/2

18 BEGIN

19 IF(clr = '0')THEN

20 count: = 0;

21 time_tempi < = '0';

22 ELSIF(clk_in'eventand clkin = '1')THEN

23 IF(count = 16384)THEN

24 count: = 0;

25 time_temp1 < = '1';

26 ELSE

27 count: = count + 1;

28 time_temp1 < = '0';

29 END IF;

30 END IF;

31 END PROCESS;

32

33 PROCESS(clr, time_temp1)

34 BEGIN

35 IF(clr = '0')THEN

36 time temp2<= '0';

37 ELSIF(time_temp1'event AND time_temp1='1')THEN

38 time_temp2<=NOT time_temp2;

39 END IF;

40 END PROCESS;

41 clk_out<=time_temp2 ;

END fre_architecture;

4)秒计数器

秒计数器是六十进制计数器,有3个输入信号和4个输出信号。为了实现整点报时功能,设计了2个秒报时控制信号,具体是:当计数到54时,报时控制信号second_alarm1为高电平;当计数达到59时,报时控制信号second_alarm2为高电平;当计数达到60时,计数器归零,输出1个秒一分钟的选通信号,重新进行计数。

秒计数器的VHDL源程序如下:

1 LIBRARY IEEE;

2 USE IEEE. STD_LOGIC_II64.ALL;

3 USE IEEE. STD_LOGIC_ARITH. ALL;

4 ENTITY second IS

5 PORT(

6 clk_in : IN STD_LOGIC;

7 clr : IN STD_LOGIC;

8 cs : IN STD_LOGIC;

9 second led out : OUT STD_LOGIC_VECTOR(5 DOWNTO 0);

10 clk_second to minute: OUT STDLOGIC; --秒向分钟模块的进位信号

11 second alarml: OUT STD LOGIC; --报警控制输出信号1

12 second_alarm2: OUT STD_LOGIC --报警控制输出信号2

14 END second;

15 ARCHITECTURE second architecture OF second IS

16 SIGNAL counterl:INTEGER RANGE 0 TO 60;

17 BEGIN

18 PROCESS(clr, clk_in)

19 VARIABLE counter:INTEGER RANGE 0 TO 60;

20 BEGIN

21 IF(clr = '0')THEN

22 counter: = 0;

23 ELSIF(clk_in'event AND clk_in= '1')THEN

24 IF(cs = '1' )THEN

25 counter : = counter + 1 ;

26 IF ( counter = 54 ) THEN

27 second_alarm1 <= '1' ; --到54秒时,输出控制信号1

28 ELSIF( counter = 59 ) THEN

29 clk second to minute<= '1';

30 second alarm1 <= '0';

31 second_alarm2 < = '1'; --到59秒时,输出控制信号2

32 ELSIF( counter = 60 ) THEN

33 counter: = 0;

34 clk_second_to_minute<= '0'; --时钟进位

35 second alarm1 < = '0'

36 second alarm2< = '0';

37 END IF;

38 END IF;

39 END IF;

40 counter1 < = counter;

41 END PROCESS;

42 second_led_out < = CONV_STD_LOGIC_VECTOR(counter1, 6) ;

43 END second_architecture;

秒计数器的仿真时序如图所示。当秒计数器计数到54时,second_alarm1输出高电平;在59秒时,second_alarm1为低电平,而second_alarm2被置为高电平,同时输出1个clk_second_to_minute的高电平脉冲信号。在下一个时钟沿到来时,秒计数器被归0。

5)分计数器

分计数器是六十进制计数器,它有3个输入和3个输出,如图9-17所示。为了实现整点报时功能,设计了1个报时控制信号。当计数到59时,报时控制信号minute_alarm为高电平;当计数达到60时,分计数器归0,输出一个脉冲控制信号作为“时”计数器的进位信号,分计数器重新进行计数。

分计数器的VHDL源程序如下:

1 LIBRARY IEEE;

2 USE IEEE. STD_LOGIC_1164.ALL;

3 USE IEEE. STD_LOGIC_ARITH. ALL;

4 ENTITY minute IS

5 PORT(

6 clk_in : IN STD_LOGIC;

7 clr : IN STD_LOGIC;

8 cs : IN STD_LOGIC;

9 minute led out : OUT STD_LOGIC_VECTOR(5 downto 0);

10 clk minute to hour : OUT STD_LOGIC; --向小时模块的进位

11 minute_alarm: OUT STD_LOGIC

12 );

13 END minute;

14 ARCHITECTURE minute_architecture OF minute IS

15 SIGNAL counter1:INTEGERRANGE 0 TO 60;

16 BEGIN

17 PROCESS(clr, clk_in)

18 VARIABLE counter:INTEGER RANGE 0 TO 60;

19 BEGIN

20 IF(clr = '0')THEN

21 counter: = 0;

22 ELSIF(clk_in'event AND clk_in = '1')THEN

23 IF(cs = '1')THEN

24 counter: = counter + 1;

25 IF(counter = 59)THEN

26 minute_alarm<= '1';

27 clk_minute_to_hour< = '1';

28 ELSIF(counter > = 60)THEN

29 counter: = 0;

30 minute_alarm<= '0';

31 clk_minute_to_hour<= '0';

32 END IF;

33 END IF;

34 END IF;

35 counter1 < = counter;

36 END PROCESS;

37 minute_led_out < = CONV_STD_LOGIC_VECTOR(counter1,6);

38 END minute_architecture;

分计数器的仿真时序如图9-18所示。当counter1加到59时,clk_minute_to_hour输出“1”;下一个脉冲到来时,分计数器归0。

6)时计数器

“时”计数器是二十四进制计数器,它有3个输入和1个输出,如图9-19所示。当计数达到24时,时计数器归0,并重新进行计数。

时计数器的VHDL源程序如下:

1 LIBRARY IEEE;

2 USE IEEE. STD_LOGIC_1164. ALL;

3 USE IEEE. STD_LOGIC_ARITH. ALL;

4 ENTITY hour IS

5 PORT(

6 clk_in : IN STD_LOGIC; --时钟

7 clr : IN STD LOGIC;

8 cs : INSTD LOGIC; --片选

9 hour_led_out : OUT STD_LOGIC_VECTOR(5 DOWNTO 0) --小时输出显示

10 );

11 END hour;

12 ARCHITECTURE hour architecture OF hour IS

13 SIGNAL counter1 :INTEGER RANGE 0 TO 24;

14 BEGIN

15 PROCESS( clr, clk_in)

16 VARIABLE counter:INTEGER RANGE 0 TO 24;

17 BEGIN

18 IF(clr = '0' ) THEN

19 counter: = 0;

20 ELSIF(clk_in'event AND clk_in = '1')THEN

21 IF(cs= '1')THEN

22 counter: = counter + 1;

23 END IF;

24 IF(counter = 24) THEN

25 counter: = 0;

26 END IF;

27 END IF;

28 counter1 < = counter;

29 END PROCESS;

30 hour_led_out<= CONV STD LOGIC_VECTOR(counter1, 6);

31 END hour architecture;

时计数器的仿真时序如图9-20所示,当时计数器达到23时,下一个时钟沿到来时,时计数器被归0。

7)译码电路

为了在七段数码管上显示时、分、秒计数器的输出信号(6位二进制数),需要将6位二进制数输入转换成两个4位二进制输出。因此,译码电路的输入和输出如图9-21所示。输入信号范围是0~59,4位二进输出信号范围是0~9。 译码电路的VHDL源程序如下:

译码电路的VHDL源程序如下:

1 LIBRARY IEEE;

2 USE IEEE. STD_LOGIC_1164. ALL;

3 USE IEEE. STD_LOGIC_UNSIGNED. ALL;

4 USE IEEE. STD_LOGIC_ARITH. ALL;

5

6 ENTITY decoder IS

7 PORT(

8 data:IN STD_LOGIC_VECTOR(5 DOWNTO 0); --输入数据

9 ten:OUT STD LOGIC_VECTOR(3 DOWNTO 0); --十位数据

10 one:OUT STD_LOGIC_VECTOR(3 DOWNTO 0) --个位数据

11 );

12 END;

13

14 ARCHITECTURE arch OF decoder IS

15 BEGIN

16 PROCESS (data)

17 VARIABLE counter_ten:INTEGER RANGE 0 TO 15;

18 VARIABLE counter_one:INTEGER RANGE 0 TO 15;

19 BEGIN

20 counter_ten: = 0 ;

21 counter_one: = 0;

22 IF(data(0) ='1')THEN

23 counter_one: = counter_one + 1; --最低位为1时,个位值加1

24 IF ( counter_one > 9 ) THEN

25 counter_one: =counter_one+6; --值超过9,需要加6调整

26 counter_ten: = counter_ten+ 1; --同时十位值加1

27 END IF;

28 END IF;

29 IF(data(1) = '1' ) THEN

30 counter_one: = counter_one + 2; --第一位为1,个位加2

31 IF(counter_one > 9 ) THEN

32 counter_one: = counter_one + 6;

33 counter_ten: = counter_ten + 1;

34 END IF;

35 END IF;

36 IF(data(2) = '1')THEN

37 counter_one: = counter_one + 4; --第二位为1,个位加4

38 IF(counter_one> 9 ) THEN

39 counter_one: = counter_one + 6;

40 counter_ten: = counter_ten + 1 ;

41 END IF;

42 END IF;

43 IF(data(3) = '1')THEN

44 counter_one: = counter_one + 8; --第三位为1,个位加8

45 IF( counter_one > 9 ) THEN

46 counter one: = counter_one + 6;

47 counter_ten: = counter_ten + 1;

48 END IF;

49 END IF;

50 IF(data(4) = '1')THEN

51 counter_one: = counter_one+ 6; --第四位为1,个位加6

52 counter_ten: = counter_ten + 1; --同时十位数字加1

53 IF ( counter_one > 9 ) THEN

54 counter_one: = counter_one + 6;

55 counter_ten: = counter_ten + 1;

56 END IF;

57 END IF;

58 IF(data(5) = '1')THEN

59 counter_one: =counter_one+2; --最高位为1,个位数字加2

60 counter_ten: = counter_ten + 3; --同时十位数字加3

61 IF( counter_one > 9 ) THEN

62 counter_ one: = counter_one + 6;

63 counter_ten : = counter_ten + 1 ;

64 END IF;

65 END IF;

66 ten<= CONV_STD_LOGIC_VECTOR(counter_ten, 4); --变量转为向量值

67 one < = CONV_STD_LOGIC_VECTOR(counter_one, 4) ;

68 END PROCESS;

69

70 END arch。

8)显示模块

显示模块的输入信号为译码电路的输出信号,是一个4位二进制信号。显示模块的输出连接一个七段数码管。因此,显示模块的VHDL源程序如下:

1 LIBRARY IEEE;

2 USE IEEE. STD_LOGIC_II64. ALL;

3 USE IEEE. STD_LOGIC_UNSIGNED. ALL;

4

5 ENTITY display IS

6 PORT(

7 data: IN STD_LOGIC_VECTOR ( 3 DOWNTO 0) ;

8 play:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

9 );

10 END;

11

12 ARCHITECTURE arch OF display IS

13 BEGIN

14 PROCESS(data)

15 BEGIN

16 CASE data IS

17 WHEN "0000" = > play < = "1000000" ; -- ----t----

18 WHEN "0001" = > play < = "1111001" ; -- | |

19 WHEN "0010" = > play < = "0100100" ; -- lt rt

20 WHEN "0011" = > play < = "0110000" ; -- | |

21 WHEN "0100" = > play < = "0011001" ; -- ----m----

22 WHEN "0101" = > play < = "0010010" ; -- | |

23 WHEN "0110" = > play < = "0000010" ; -- lb rb

24 WHEN "0111" = > play < = "1111000" ; -- | |

25 WHEN "1000" = > play < = "0000000" ; -- ----b----

26 WHEN "1001" = > play < = "0010000" ;

27 WHEN "1010" = > play < = "0001000" ;

28 WHEN "1011" = > play < = "0000011" ;

29 WHEN "1100" = > play < = "1000110" ;

30 WHEN "1101" = > play < = "0100001" ;

31 WHEN "1110" = > play < = "0000110" ;

32 WHEN "1111" = > play < = "0001110" ;

33 WHEN OTHERS = > play < = "0000000" ;

34 END CASE;

35 END PROCESS;

36 END arch;

9)整点报时电路

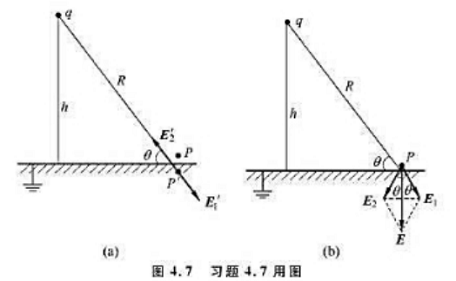

当分计数器在每次计时到整点的前6秒时,开始整点报时。也就是,当“分”计数器在59分,“秒”计数器在54秒时,要求整点报时电路发出控制信号F1,该信号持续时间为5s;当时钟运行到59分59秒时,整点报时电路发出另一个控制信号F2,该信号持续时间为1s。因此,整点报时电路有3个输入和2个输出,如图9-23所示。

整点报时电路的VHDL源程序如下:

1 LIBRARY IEEE;

2 USE IEEE. STD_LOGIC_1164.ALL;

3 USE IEEE. STD_LOGIC_UNSIGNED. ALL;

4

5 ENTITY alarm IS

6 PORT

7 (

8 minute_alarm:IN STD_LOGIC; --分计数器为59时报警信号

9 second_alarm1 : IN STD_LOGIC; --秒计数器为54时报警信号

10 sec0nd_alarm2:IN STD_LOGIC; --秒计数器为59时报警信号

11 F1:OUT STD_LOGIC; --59分54秒输出信号

12 F2:OUT STD_LOGIC -- 59分59秒输出信号

13 );

14 END alarm;

15 ARCHITECTUHEarch OF alarm IS

16 BEGIN

17 PROCESS(minute_alarm, second_alarm1, second_alarm2)

18 BEGIN

19 IF(minute_alarm = '1')THEN

20 IF ( second_alarm1 = '1' ) THEN

21 F1<= '1';

22 F2<= '0';

23 ELSIF ( second alarm2 = '1' ) THEN

24 F1<= '0';

25 F2<= '1';

26 END IF;

27 ELSE

28 F1 < = '0';

29 F2 < = '0';

30 END IF;

31 END PROCESS;

32 END arch。

10)系统实现

在DE2_70开发平台上,外接32768Hz输入信号进行测试,6个数码管分别显示数字钟的时、分、秒。“秒”计数器的个位计数器从0开始计数,当个位计数到9时,在下一个时钟到来时,秒计数器的个位被清零,秒计数器的十位加1;当秒计数器的十位计数到5、个位为9,在下一个时钟到来时,秒计数器的个位和十位均被清零,分计数器的个位加1。

同理,分计数器在计数到59、秒计数到54时,F1输出高电平;当分计数器计数到59、秒计数器计数到59时,F1输出低电平、F2输出高电平。在下一个秒脉冲到来时,分、秒计数器均被清零,时计数器自动加1。

在系统运行过程中,可以对数字钟进行时间调整。在输入使能端en为高电平时,每拨动一下time_select端口,可以分别对数字钟的秒、分、时进行调整。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“试设计一个数字电子钟,其原理框图如图9-10所示。秒信号用石…”相关的问题

更多“试设计一个数字电子钟,其原理框图如图9-10所示。秒信号用石…”相关的问题

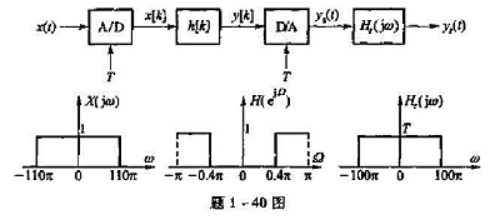

的频谱。

的频谱。