题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

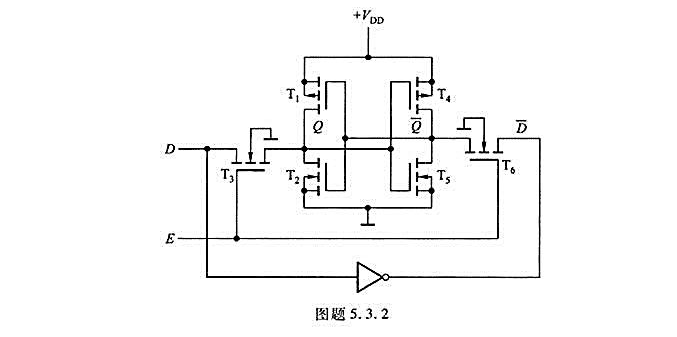

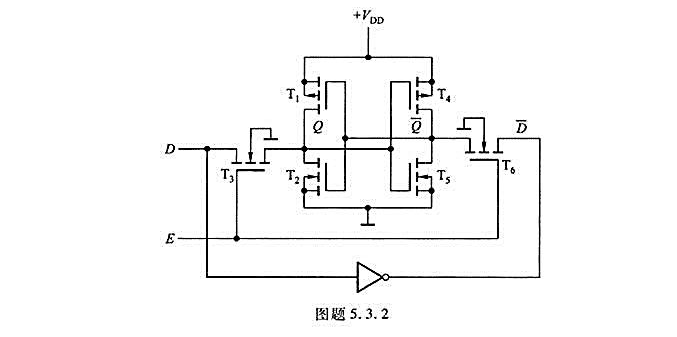

一种简单的D锁存器晶体管级电路如图题5.3.2所示,试列出该电路的功能表。这种电路广泛用于CMOS静

态随机存储器(SRAM)中作为基本存储单元。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“一种简单的D锁存器晶体管级电路如图题5.3.2所示,试列出该…”相关的问题

更多“一种简单的D锁存器晶体管级电路如图题5.3.2所示,试列出该…”相关的问题

A.TSPCR的功能受晶体管尺寸的影响大

B.C^2MOS是一种单相时钟技术,提供了一种允许时钟偏差的解决办法

C.TSPCR可以将逻辑功能嵌入到锁存器中

D.C^2MOS锁存器在时钟斜率不够陡直时不能正确工作

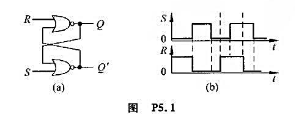

画出图P5.1(a)中SR锁存器Q和Q'端的电压波形。输入端S和R的电压波形如图P5.1(b)所示。

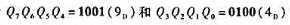

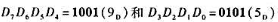

试用1片八D锁存器74HC373设计一个能锁存两组BCD码信号的锁存电路。假定三态输出使能端 ,锁存器原输出为

,锁存器原输出为 ,输入为

,输入为 ,画出锁存器锁存新数据前、后使能端LE应输入的波形和相应Q0的波形。

,画出锁存器锁存新数据前、后使能端LE应输入的波形和相应Q0的波形。

如图题5.17所示的差分电路中,已知u1(t)=360cos(2π×105t)(mV),u2(t)=10cos(2π×103t)(mV),VCC=VEE=10V,REE=10kΩ,晶体管的β很大,UBE(on)可忽略。试用开关函数求iC(t)=iC1(t)-iC2(t)的关系式。