题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

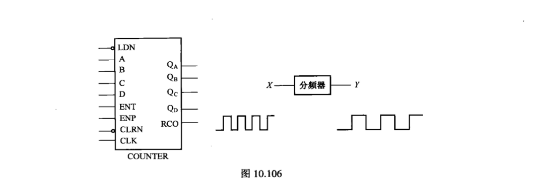

某逻辑电路的输入为x,输出为Z。当x在连续四个时钟周期内输入为全0或全1时,输出Z为1;否则,输出Z为0。画出该电

路的算法流程图。

答案

答案

算法流程图,如图所示。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

路的算法流程图。

答案

答案

算法流程图,如图所示。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“某逻辑电路的输入为x,输出为Z。当x在连续四个时钟周期内输入…”相关的问题

更多“某逻辑电路的输入为x,输出为Z。当x在连续四个时钟周期内输入…”相关的问题

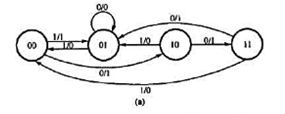

图3.12(a)是某时序电路的状态转换图,设电路的初始状态为01,当序列X=100110(自左至右输入)时,求该电路输出Z的序列.

(1)证明当x在[0,2π]均匀分布时,信道达到容量。

(2)对下列两种情况求信道容量C;

1 ,其他

,其他

2

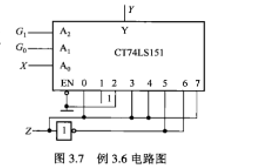

设X,Y均为4位二进制数,它们分别是一个逻辑电路的输入与输出,当0≤X≤4时,Y=X+1;当5≤X≤9时,Y=X-1,且X不大于9。试用与非门实现该电路。

有一叠加性噪声的信道,输入符号x是离散的,取值+1或-1,噪声N的概率密度为 则输出的Y=X+N是一个连续变量。

则输出的Y=X+N是一个连续变量。

(1)求这一半连续信道的容量。

(2)若在输出端接一检测器也作为信道的一部分,检测输出变量为Z有当Y >1,则Z=1;1≥Y≥-1,则Z=0; Y<-1,则Z=-1,这就成为了一个离散信道,求它的容量。

(3)若检测特性改为:当Y≥0,则Z=1;当Y<0,则Z=-1.求这离散估道的容量。

(4)从上面结果可见,(2)的检测器无信息损失,而(3)则不然:若噪声特性改为 试构成一个不损失信息的检测器。

试构成一个不损失信息的检测器。

A.当X为连续性数据,而Y是离散数据时的分析

B.当Y为连续性数据,而X是离散数据时的分析

C.输入变量和输出变量的因果关系

D.输入变量和输出变量的相关性